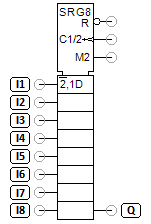

8-bit shift register, parallel-serial

With the shift register, data (8 bits) can be entered in parallel format and converted into a stream of serial bits. The bits are stored in the registers R1 to R8 and output via the output Q.

The output mode is activated when the value 1 is present at input M. The contents of each register are then shifted to the subsequent register with each rising edge from 0 to 1 at input C. The contents of register R8 are shifted to register R1 in the ring.

The registers are loaded via the inputs I1 to I8. The registers accept the values of the inputs if the value 0 is present at input M and there is a rising edge from 0 to 1 at input C.

The shift register also has an inverted input R for reset, i.e. R=0 sets all registers to 0.

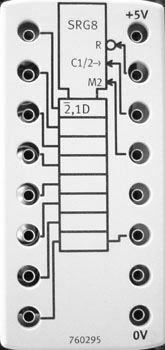

The IC 74HC166 is used as a component in the training package TP 1012 from Festo Didactic.

Adjustable parameters

| Designation | Range | Default value |

|---|---|---|

| Voltage level (lo) | 0.1 ... 24 V | 0.8 |

| Voltage level (hi) | 0.1 ... 24 V | 2 |

| Designation | Range | Default value |

|---|---|---|

| Voltage level (lo) | 0 ... 24 V | 0 |

| Voltage level (hi) | 0.1 ... 24 V | 5 |

| Resistance | 0.1 ... 1000 Ohm | 55 |