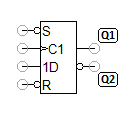

D flip-flop with SET and RESET inputs, edge triggered

This D flip-flop is an edge-triggered D flip-flop with two additional inputs S and R. With the input S (set), the internal state can be set directly to 1. With the input R (reset), the internal state can be set directly to 0. The inputs S and R are inverted, i.e. the value 1 triggers the set or reset.

Truth table

| not S | not R | C | D | Q1 | Q2 |

|---|---|---|---|---|---|

| 0 | 1 | x | x | 1 | 0 |

| 1 | 0 | x | x | 0 | 1 |

| 0 | 0 | x | x | 1 | 1 |

| 1 | 1 | ↑ | 0 | 0 | 1 |

| 1 | 1 | ↑ | 1 | 1 | 0 |

| 1 | 1 | x | x | q1 | q2 |

Comments:

x = any (0 or 1) ↑ = positive edge from 0 to 1 q = state of output Q remains unchanged

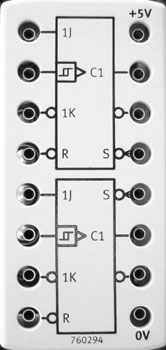

The IC 74HC74 is used as a component in the training package TP 1012 from Festo Didactic.

Adjustable parameters

| Designation | Range | Default value |

|---|---|---|

| Voltage level (lo) | 0.1 ... 24 V | 0.8 |

| Voltage level (hi) | 0.1 ... 24 V | 2 |

| Designation | Range | Default value |

|---|---|---|

| Voltage level (lo) | 0 ... 24 V | 0 |

| Voltage level (hi) | 0.1 ... 24 V | 5 |

| Resistance | 0.1 ... 1000 Ohm | 50 |