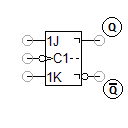

JK MS flip-flop

A JK MS flip-flop (JK master/slave flip-flop) is a clock-skewed JK flip-flop. With the rising edge at the clock input, the flip-flop transfers the input information to a buffer. This new state is not forwarded to the output until the falling edge.

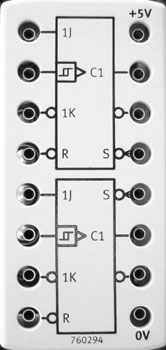

In the circuit diagram TP1012_05_3a2.circ

, implementation of the JK MS flip-flop is shown with two JK flip-flops and an inverter.

Adjustable parameters

| Designation | Range | Default value |

|---|---|---|

| Voltage level (lo) | 0.1 ... 24 V | 0.8 |

| Voltage level (hi) | 0.1 ... 24 V | 2 |

| Designation | Range | Default value |

|---|---|---|

| Voltage level (lo) | 0 ... 24 V | 0 |

| Voltage level (hi) | 0.1 ... 24 V | 5 |

| Resistance | 0.1 ... 1000 Ohm | 50 |