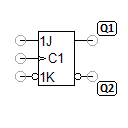

JK flip-flop, edge triggered, K inverted

With this JK flip-flop the input K is inverted. If there is a NOT gate upstream of the input K, this flip-flop behaves in exactly the same way as the standard JK flip-flop.

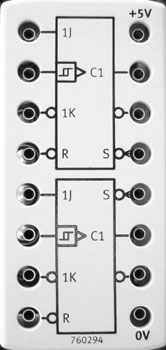

Adjustable parameters

| Designation | Range | Default value |

|---|---|---|

| Voltage level (lo) | 0.1 ... 24 V | 0.8 |

| Voltage level (hi) | 0.1 ... 24 V | 2 |

| Designation | Range | Default value |

|---|---|---|

| Voltage level (lo) | 0 ... 24 V | 0 |

| Voltage level (hi) | 0.1 ... 24 V | 5 |

| Resistance | 0.1 ... 1000 Ohm | 50 |