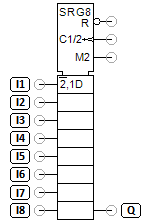

Schieberegister 8 Bit, parallel-seriell

Mit dem Schieberegister können Daten (8 Bits) parallel eingegeben und in einen Strom von seriellen Bits gewandelt werden. Die Bits werden in den Registern R1 bis R8 gespeichert und über den Ausgang Q ausgegeben.

Der Ausgabemodus ist aktiviert, wenn am Eingang M der Wert 1 anliegt. Dann wird mit jeder steigenden Flanke von 0 nach 1 am Eingang C der Inhalt jedes Registers in das nachfolgende Register verschoben. Der Inhalt vom Register R8 wird im Ring ins Register R1 verschoben.

Die Register werden über die Eingänge I1 bis I8 geladen. Die Register übernehmen die Werte der Eingänge, wenn am Eingang M der Wert 0 anliegt und eine steigende Flanke von 0 nach 1 am Eingang C auftritt.

Zusätzlich besitzt das Schieberegister noch einen invertierten Eingang R zum Zurücksetzen (englisch: Reset), d.h. R=0 setzt alle Register auf 0.

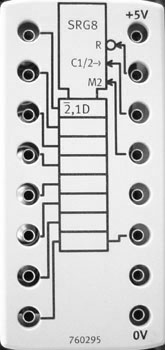

Im Technologiepaket TP 1012 von Festo Didactic wird das IC 74HC166 als Bauteil verwendet.

Einstellbare Parameter

| Bezeichnung | Bereich | Standardwert |

|---|---|---|

| Spannungspegel (lo) | 0.1 ... 24 V | 0.8 |

| Spannungspegel (hi) | 0.1 ... 24 V | 2 |

| Bezeichnung | Bereich | Standardwert |

|---|---|---|

| Spannungspegel (lo) | 0 ... 24 V | 0 |

| Spannungspegel (hi) | 0.1 ... 24 V | 5 |

| Widerstand | 0.1 ... 1000 Ohm | 55 |