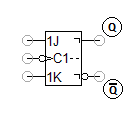

JK-MS-Flipflop

Ein JK-MS-Flipflop (JK-Master/Slave-Flipflop) ist ein zweiflankengesteuertes JK-Flipflop. Durch die steigende Flanke am Takteingang übernimmt das Flipflop die Eingangsinformation in einen Zwischenspeicher. Erst durch die fallende Taktflanke wird dieser neue Zustand an den Ausgang weitergeleitet.

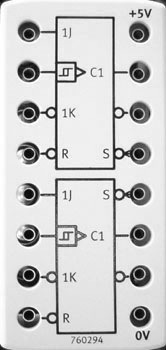

Im Schaltplan TP1012_05_3a2.circ

ist die Realisierung des JK-MS-Flipflops mit zwei JK-Flipflops und einem Inverter aufgezeigt.

Einstellbare Parameter

| Bezeichnung | Bereich | Standardwert |

|---|---|---|

| Spannungspegel (lo) | 0.1 ... 24 V | 0.8 |

| Spannungspegel (hi) | 0.1 ... 24 V | 2 |

| Bezeichnung | Bereich | Standardwert |

|---|---|---|

| Spannungspegel (lo) | 0 ... 24 V | 0 |

| Spannungspegel (hi) | 0.1 ... 24 V | 5 |

| Widerstand | 0.1 ... 1000 Ohm | 50 |